**Data Sheet**

July 2004

**Features**

- QPSK tuner for quadrature down conversion from L-band to Zero IF

- Compatible with DSS and DVB formats (QPSK)

- Symbol rate range 1 to 45 MSps

- Power & forget, fully integrated, alignment free, local oscillator

- Integrated baseband filters with bandwidth adjust from 4 to 40 MHz

- Good immunity to strong adjacent undesired channels

- · Selectable RF bypass

- I<sup>2</sup>C bus interface with 3V3 compatible logic levels

- Integrated RF loop through for cascaded tuner applications

- · Power saving mode/hardware power down

- Optimized front end solution when partnered with Zarlink ZL10312 demodulator

# **Applications**

· Satellite receiver systems

# Ordering Information

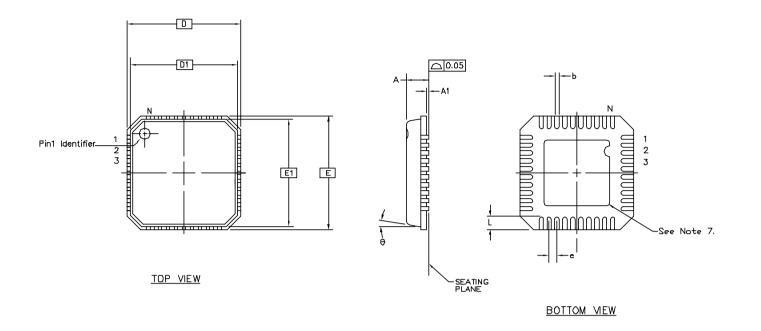

ZL10036LDG 40-pin QFN (trays)

ZL10036LDF 40-pin QFN (tape and reel)

ZL10036LDG1 40-pin QFN\* (trays)

ZL10036LDF1 40-pin QFN\* (tape and reel)

\*Pb free -10°C to +85°C

# Description

The ZL10036 is a single chip wideband direct conversion tuner, with integral RF bypass, optimized for application in digital satellite receiver systems.

The device offers a highly integrated solution to a satellite tuner function, incorporating an I<sup>2</sup>C bus interface controller, a low phase noise PLL frequency synthesizer, a quadrature phase split tuner, a fully integrated local oscillator which requires no production set up, and adjustable baseband channel filters.

The I<sup>2</sup>C bus interface controls all of the tuner functionality including the PLL frequency synthesizer, the bypass disable and the baseband gain and bandwidth adjust.

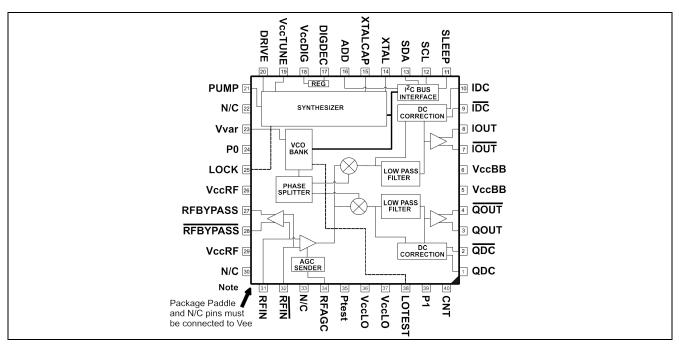

Figure 1 - Basic Block Diagram

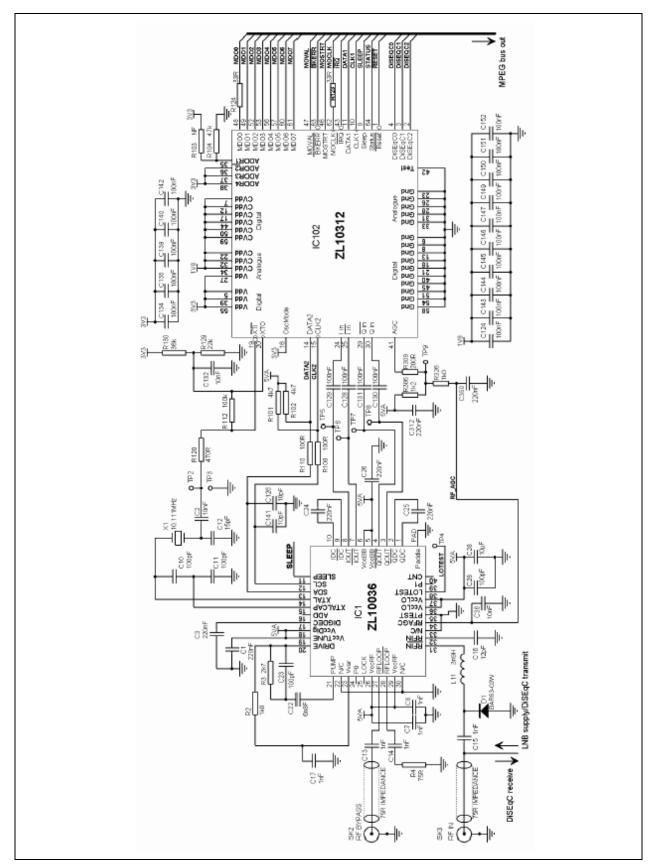

Figure 2 - Typical Application Circuit ZLE10532 (SNIM-9r2) using ZL10312 Demodulator

# **Table of Contents**

|     | Overview                                                    |      |

|-----|-------------------------------------------------------------|------|

|     | 1.1 Conventions in this Manual                              | . 11 |

| 2.0 | Functional Description                                      | . 12 |

|     | 2.1 Quadrature Down-Converter                               |      |

|     | 2.2 AGC Functions                                           |      |

|     | 2.2.1 RF                                                    |      |

|     | 2.2.2 Baseband                                              |      |

|     | 2.3 RF bypass                                               |      |

|     | 2.4 Baseband Filter                                         |      |

|     |                                                             |      |

|     | 2.5 Local Oscillator                                        |      |

|     | 2.6 PLL Frequency Synthesizer                               |      |

|     | 2.7 Control Logic                                           |      |

|     | User Control                                                |      |

|     | 3.1 I/O Pins                                                | . 19 |

|     | 3.1.1 LOCK - Pin 25                                         | . 19 |

|     | 3.1.2 SLEEP - Pin 11                                        |      |

|     | 3.1.3 Output Ports, P1 & P0 - Pins 39 & 24                  | . 19 |

|     | 3.2 Device Address Selection                                |      |

|     | 3.3 Read Register                                           |      |

|     | 3.3.1 Power-On Reset Indicator (POR bit)                    |      |

|     | 3.3.2 Frequency & Phase Lock (FL bit)                       |      |

|     | 3.3.3 Internal Operation Indicators (X Bits).               |      |

|     | 3.4 Write Registers                                         |      |

|     | 3.4.1 Register Sub-Addressing                               |      |

|     |                                                             |      |

|     | 3.4.2 Register Mapping                                      | . 22 |

|     | 3.4.4 RF Gain (RFG Bit)                                     | . 23 |

|     | 3.4.5 Baseband Pre-Filter Gain Adjust (BA1:0 Bits)          |      |

|     |                                                             |      |

|     | 3.4.6 Baseband Post-Filter Gain (BG1:0 Bits)                |      |

|     | 3.4.7 RF Bypass Disable (LEN Bit)                           |      |

|     | 3.4.8 Output Port Controls (P1 & P0 Bits).                  |      |

|     | 3.4.9 Power Down (PD Bit)                                   |      |

|     | 3.4.10 Logic Reset (CLR Bit)                                |      |

|     | 3.4.11 Charge Pump Current (C1 & C0 Bits)                   |      |

|     | 3.4.12 Reference Division Ratios (R4:0 Bits)                |      |

|     | 3.4.13 Baseband Filter Resistor Switching (RSD)             |      |

|     | 3.4.14 Baseband Filter Bandwidth (BF6:1 & BR4:0 Bits)       |      |

|     | 3.4.15 LO Test (TL Bit)                                     | . 25 |

| 4.0 | Software                                                    | . 26 |

|     | 4.1 Power-on Software Initialization                        | . 26 |

|     | 4.2 Changing Channel                                        |      |

|     | 4.3 Symbol Rate and Filter Calculations                     | . 26 |

|     | 4.3.1 Determining the Filter Bandwidth from the Symbol Rate |      |

|     | 4.3.2 Calculating the Filter Bandwidth                      |      |

|     | 4.3.3 Determining the Values of BF and BR                   |      |

|     | 4.3.3.1 Calculating the Value of BR                         |      |

|     | 4.3.3.2 Calculating the Value of BF                         |      |

|     | 4.3.4 Filter Bandwidth Programming Examples                 |      |

|     | 4.4 Programming Sequence for Filter Bandwidth Changes       |      |

|     |                                                             |      |

|     | Application Notes                                           |      |

|     | 5.1 Thermal Considerations                                  |      |

|     | 5.2 Crystal Oscillator Notes                                | . 30 |

# **Table of Contents**

| 3.0 | Electrical characteristics           | 3 | 31 |

|-----|--------------------------------------|---|----|

|     | 6.1 Test Conditions                  | 3 | 31 |

|     | 6.2 Absolute Maximum Ratings         | 3 | 31 |

|     | 6.3 Recommended Operating Conditions | 3 | 32 |

|     | 6.4 DC Characteristics               | 3 | 32 |

|     | 6.5 AC Characteristics               |   | 33 |

# **List of Figures**

| Figure 1 - Basic Block Diagram                                                       | 1  |

|--------------------------------------------------------------------------------------|----|

| Figure 2 - Typical Application Circuit ZLE10532 (SNIM-9r2) using ZL10312 Demodulator | 2  |

| Figure 3 - Functional Block Diagram                                                  | 12 |

| Figure 4 - AGC Control Structure                                                     | 13 |

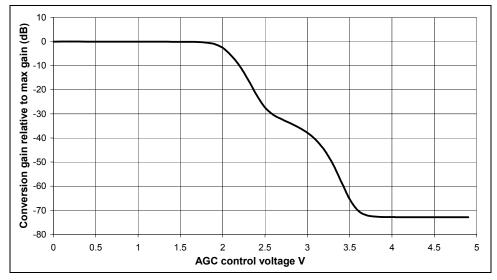

| Figure 5 - Typical First Stage RF AGC Response                                       | 13 |

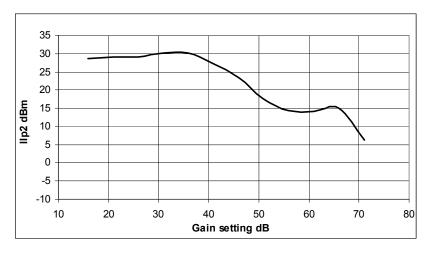

| Figure 6 - Variation in IIP2 with AGC setting                                        | 14 |

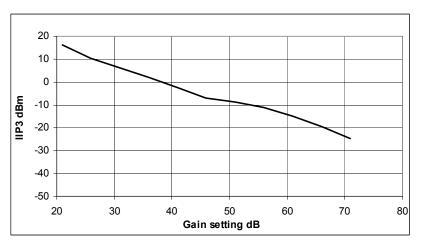

| Figure 7 - Variation in IIP3 with AGC setting                                        | 14 |

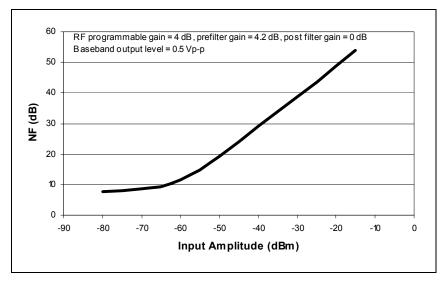

| Figure 8 - Variation in NF with Input Amplitude (typical)                            | 15 |

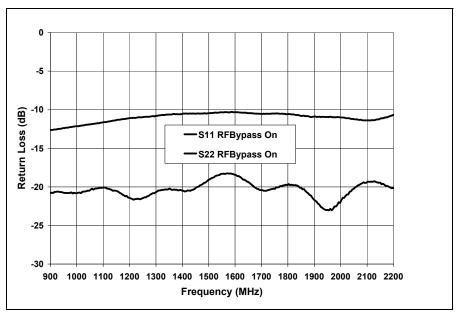

| Figure 9 - RF input and Output (bypass) Return Losses                                |    |

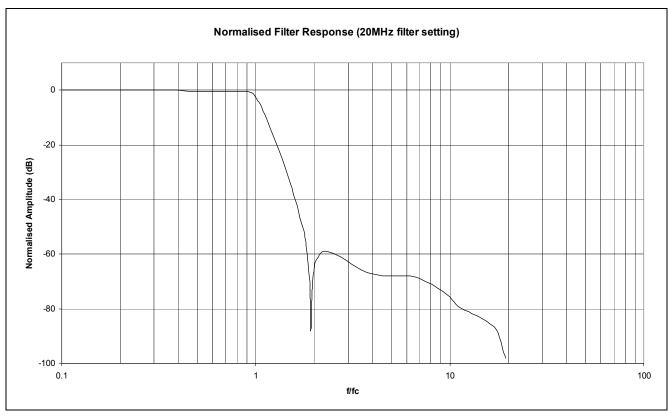

| Figure 10 - Normalized Filter Transfer Characteristic (Setting 20 MHz)               | 17 |

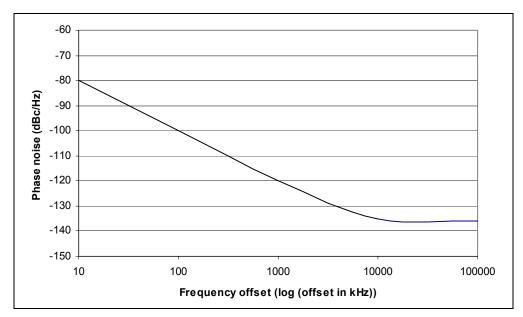

| Figure 11 - LO Phase Noise Performance                                               |    |

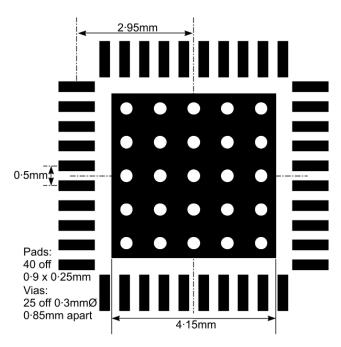

| Figure 12 - Copper Dimensions for Optimum Heat Transfer                              | 29 |

| Figure 13 - Paste Mask for Reduced Paste Coverage                                    | 29 |

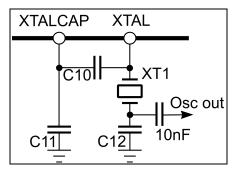

| Figure 14 - Typical Oscillator Arrangement with Optional Output                      | 30 |

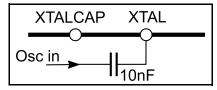

| Figure 15 - Typical Arrangement for External Oscillator                              |    |

# **List of Tables**

| Table 1 - Pins by Number Order                                         | 7  |

|------------------------------------------------------------------------|----|

| Table 2 - Pins by Name Order                                           | 7  |

| Table 3 - Address Selection                                            | 20 |

| Table 4 - Read Data Bit Format (MSB is Transmitted First)              | 20 |

| Table 5 - Byte Address Allocation in Write Mode                        | 21 |

| Table 6 - Bit Allocations in the Write Registers                       | 22 |

| Table 7 - Key to Table 6                                               | 22 |

| Table 8 - RFG Register Bit Function                                    | 23 |

| Table 9 - BA1/0 Register Bits Function                                 | 23 |

| Table 10 - BG1/0 Register Bits Function                                | 23 |

| Table 11 - Port Control Bits                                           | 24 |

| Table 12 - Charge Pump Currents                                        | 24 |

| Table 13 - Division Ratios Set with Bits R4 - R0                       | 25 |

| Table 14 - Crystal Capacitor Values for 4 MHz and 10.111 MHz Operation | 30 |

|                                                                        |    |

# Pin Listings

| No. | Name  | No. | Name    | No. | Name     | No. | Name   |

|-----|-------|-----|---------|-----|----------|-----|--------|

| 1   | QDC   | 11  | SLEEP   | 21  | PUMP     | 31  | RFIN   |

| 2   | QDC   | 12  | SCL     | 22  | N/C      | 32  | RFIN   |

| 3   | QOUT  | 13  | SDA     | 23  | Vvar     | 33  | N/C    |

| 4   | QOUT  | 14  | XTAL    | 24  | P0       | 34  | RFAGC  |

| 5   | VccBB | 15  | XTALCAP | 25  | LOCK     | 35  | PTEST  |

| 6   | VccBB | 16  | ADD     | 26  | VccRF    | 36  | VccLO  |

| 7   | IOUT  | 17  | DIGDEC  | 27  | RFBYPASS | 37  | VccLO  |

| 8   | IOUT  | 18  | VccDIG  | 28  | RFBYPASS | 38  | LOTEST |

| 9   | ĪDC   | 19  | VccTUNE | 29  | VccRF    | 39  | P1     |

| 10  | IDC   | 20  | DRIVE   | 30  | N/C      | 40  | CNT    |

Table 1 - Pins by Number Order

| Name   | No. | Name  | No. | Name     | No. | Name    | No. |

|--------|-----|-------|-----|----------|-----|---------|-----|

| ADD    | 16  | N/C   | 22  | QOUT     | 4   | VccBB   | 6   |

| CNT    | 40  | N/C   | 30  | RFAGC    | 34  | VccDIG  | 18  |

| DIGDEC | 17  | N/C   | 33  | RFIN     | 31  | VccLO   | 36  |

| DRIVE  | 20  | P0    | 24  | RFIN     | 32  | VccLO   | 37  |

| ĪDC    | 9   | P1    | 39  | RFBYPASS | 27  | VccRF   | 26  |

| IDC    | 10  | PTEST | 35  | RFBYPASS | 28  | VccRF   | 29  |

| IOUT   | 7   | PUMP  | 21  | SCL      | 12  | VccTUNE | 19  |

| IOUT   | 8   | QDC   | 1   | SDA      | 13  | Vvar    | 23  |

| LOCK   | 25  | QDC   | 2   | SLEEP    | 11  | XTAL    | 14  |

| LOTEST | 38  | QOUT  | 3   | VccBB    | 5   | XTALCAP | 15  |

Table 2 - Pins by Name Order

# **Pin Description**

| Pin | Symbol | Direction | Function                                                                                                                               | Schematics                     |  |  |

|-----|--------|-----------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| 1   | QDC NA |           | Q Channel DC offset correction capacitor. Configuration and value as per                                                               | Internal Baseband              |  |  |

| 2   | QDC    | NA        | application diagram (see Figure 2)                                                                                                     | Signal 10µA                    |  |  |

| 3   | QOUT   | Out       | VccBB                                                                                                                                  |                                |  |  |

| 4   | QOUT   | Out       | AC couple outputs as per applications diagram (see Figure 2)                                                                           | Output<br>1.2 mA               |  |  |

| 5   | VccBB  |           | +5 V voltage supply for Baseband                                                                                                       |                                |  |  |

| 6   | VccBB  |           | +5 V voltage supply for Baseband                                                                                                       |                                |  |  |

| 7   | IOUT   | Out       | I Channel baseband differential outputs                                                                                                | Same configuration as pins 3 & |  |  |

| 8   | IOUT   | Out       | AC couple outputs as per applications diagram (Figure 2)                                                                               | 4                              |  |  |

| 9   | IDC    | NA        | I Channel DC offset correction capacitor.                                                                                              | Same configuration as pins 1 & |  |  |

| 10  | IDC    | NA        | Configuration and value as per application diagram (Figure 2)                                                                          | 2                              |  |  |

| 11  | SLEEP  | ln        | Hardware power down input. Logic '0' – normal mode. Logic '1' - analogue sections are powered down. This function is OR'ed with the PD | SLEEP                          |  |  |

|     |        |           | control function, see section 3.1.2                                                                                                    | CMOS Digital Input             |  |  |

| 12  | SCL    | ln        | I <sup>2</sup> C serial clock input                                                                                                    | DIGDEC SDA/SCL 500k            |  |  |

| 13  | SDA    | Out       | I <sup>2</sup> C serial data input/output                                                                                              | Input 500k                     |  |  |

| Pin | Symbol   | Direction | Function                                                                                                                                                                               | Schematics              |  |  |

|-----|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| 14  | AIAL III |           | Reference oscillator crystal inputs. Selected crystal frequency must be programmed in BR4 to BR0 for correct baseband filter bandwidth operation.                                      | DIGDEC 400 Ω XTAL       |  |  |

| 15  | XTALCAP  | Out       | XTAL pin is used for external reference input via 10 nF capacitor.                                                                                                                     | XTALCAP  0.2mA          |  |  |

| 16  | ADD      | In        | Variable I <sup>2</sup> C address selection allowing the use of more than one device per I <sup>2</sup> C bus system by the voltage on this pin.  See Table 3 for programming details. | ADD Input 20k           |  |  |

| 17  | DIGDEC   | Out       | Decouple pin for internal digital 3.3 V regulator                                                                                                                                      | VccDIG                  |  |  |

| 18  | VccDIG   |           | +5 V voltage supply for digital logic                                                                                                                                                  |                         |  |  |

| 19  | VccTune  |           | Varactor tuning +5 V supply                                                                                                                                                            |                         |  |  |

| 20  | DRIVE    | Ю         | Loop amplifier output and input pins                                                                                                                                                   | CPDEC VCCTUNE PUMP J 3K |  |  |

| 21  | PUMP     | Ю         | 200p ampinior output and impat pino                                                                                                                                                    | DRIVE                   |  |  |

| 22  | N/C      |           | Not connected. Ground externally.                                                                                                                                                      |                         |  |  |

| 23  | Vvar     | ln        | LO tuning voltage input                                                                                                                                                                | Vvar 1 k Vbias          |  |  |

| Pin             | Symbol          | Direction | Function                                                                                                                                                                                 | Schematics                                        |  |  |

|-----------------|-----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|

| 24              | P0              | Out       | Switching port P0. '0' = disabled (high impedance). '1' = enabled.                                                                                                                       | P0/P1                                             |  |  |

| 25              | LOCK            | Out       | Output which indicates that phase comparator phase and frequency lock has been obtained and that the varactor voltage is within 'tune unlock' window. This powers up in logic '0' state. | LOCK  CMOS Digital Output                         |  |  |

| 26              | VccRF           |           |                                                                                                                                                                                          |                                                   |  |  |

| 27              | 27 RFBYPASS Out |           | RF Bypass differential outputs.  AC couple outputs. Matching circuitry as per applications diagram (Figure 2).                                                                           | V <sub>CCRF</sub><br>80Ω 80Ω RFBYPASS<br>RFBYPASS |  |  |

| 28 RFBYPASS Out |                 | Out       | In applications where RF Bypass is not required, pins should not be connected.                                                                                                           |                                                   |  |  |

| 29              | VccRF           |           | +5 V voltage supply for RF                                                                                                                                                               |                                                   |  |  |

| 30              | N/C             |           | Not connected. Ground externally.                                                                                                                                                        |                                                   |  |  |

| 31              | A               |           | RF differential inputs.  AC couple input.                                                                                                                                                | RFIN                                              |  |  |

| 32              |                 |           | Matching circuitry as per applications diagram.                                                                                                                                          | =                                                 |  |  |

| 33              | N/C             |           | Not connected. Ground externally.                                                                                                                                                        |                                                   |  |  |

| 34              | RFAGC           | ln        | RF analogue gain control input                                                                                                                                                           | VccRF<br>Vref<br>5k<br>RFAGC<br>20k               |  |  |

| Pin  | Symbol         | Direction                                                              | Function                                                             | Schematics                          |

|------|----------------|------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|

| 35   | PTEST          | ln                                                                     | Connected to internal circuit for monitoring die temperature         | PTEST                               |

| 36   | VccLO          |                                                                        | +5 V voltage supply for LO                                           |                                     |

| 37   | VccLO          |                                                                        | +5 V voltage supply for LO                                           |                                     |

| 38   | LOTEST         | Ю                                                                      | Bi-directional test port for accessing internal LO  AC couple input. | VccLO LOTEST  Bias                  |

| 39   | P1             | P1 Out Switching port P1 '0' = disabled (high impedance) '1' = enabled |                                                                      | Same configuration as pin 24,<br>P0 |

| 40   | CNT            |                                                                        |                                                                      |                                     |

| Note | : Exposed pado | dle on rear of                                                         | package must be connected to GND                                     |                                     |

# 1.0 Overview

# 1.1 Conventions in this Manual

Hexadecimal values are typically shown as 0xABCDEF. Binary values (usually of register bits) are shown as  $01100_2$ . All other numbers should be considered to be decimal values unless specified otherwise.

# 2.0 Functional Description

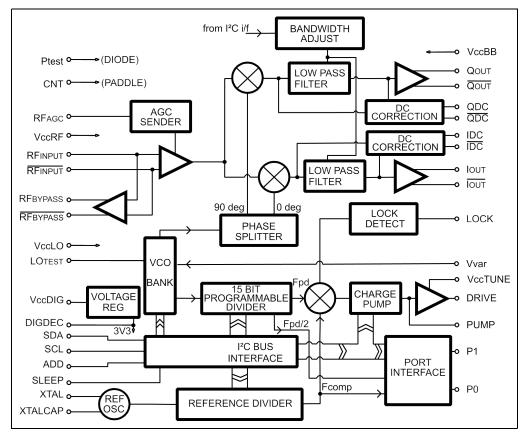

Figure 3 - Functional Block Diagram

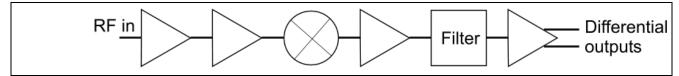

#### 2.1 Quadrature Down-Converter

In normal applications the tuner RF input frequency of 950 - 2150 MHz is fed directly to the ZL10036 RF input preamplifier stage, through an appropriate impedance match. The input preamplifier is optimized for NF, S11 and signal handling.

The signal handling of the front end is designed such that no tracking filter is required to offer immunity to input composite overload.

# 2.2 AGC Functions

The ZL10036 contains an analogue RF AGC combined with digitally controlled gain for RF, baseband pre-filter and post-filter, as described in Figure 4. The baseband AGC is controlled by the I<sup>2</sup>C bus and is divided into pre- and post-baseband filter stages, each of which have 12.6 dB of gain adjust in 4.2 dB steps.

The RF AGC is provided as the dynamic system gain adjust under control of the baseband analogue AGC output function whereas the digitally controlled gains are provided to maximize performance under different signal conditions. The total AGC gain range will guarantee an operating dynamic range of -92 to -10 dBm.

The digitally controlled RF gain adjust and the baseband pre-filter stage can be adjusted in sympathy to maintain a fixed overall conversion gain. The lower RF gain setting would be used in situations where for example there is a high degree of cable tilt or high desired to undesired ratio, whereas the higher RF gain setting would be used in situations where for example it is desirable to minimize NF.

The baseband post-filter gain stage can be used to provide additional gain to maintain desired output amplitude with lower symbol rate applications.

Figure 4 - AGC Control Structure

| Normalized gain range in dB: | 0 - 72           | 0 or +4              | 0 to 12.6 in 4.2 dB steps | 0 to 12.6 in 4.2 dB steps |

|------------------------------|------------------|----------------------|---------------------------|---------------------------|

| Gain function:               | RF AGC           | Stepped              | Stepped                   | Stepped                   |

| Control function:            | Analogue voltage | I <sup>2</sup> C bus | I <sup>2</sup> C bus      | I <sup>2</sup> C bus      |

# 2.2.1 RF

The RF input amplifier feeds an AGC stage, which provides for RF gain control.

Figure 5 - Typical First Stage RF AGC Response

The RF AGC is divided into two stages. The first stage is a continually variable gain control stage, which is controlled by the AGC sender and provides the main system AGC set under control of the analogue AGC signal generated by the demodulator section. The second stage is a bus programmable, two position gain set previous to the quadrature mixer and provides for 4 dB of gain adjust under software control.

The analogue RF AGC is optimized for S/N and S/I performance across the full dynamic range. The RF AGC characteristic, variation of IIP2, IIP3 and NF are contained in Figure 6, Figure 7 & Figure 8 respectively.

The RF preamplifier is also coupled to the selectable RF bypass, which is described in "RF bypass" on page 16. The specified electrical parameters of the RF input are unaffected by the RF bypass state.

Figure 6 - Variation in IIP2 with AGC setting

(RF gain adjust = +0 dB, prefilter = +4.2 dB and postfilter = 4.2 dB, baseband filter bandwidth = 22 MHz)

Figure 7 - Variation in IIP3 with AGC setting

(RF gain adjust = +0 dB, prefilter = +4.2 dB and postfilter = 4.2 dB, baseband filter bandwidth = 22 MHz)

Figure 8 - Variation in NF with Input Amplitude (typical)

The output of the RF AGC stage is coupled to the quadrature mixer where the RF input is mixed with quadrature LO (local oscillator) signals generated by the on-board LO.

#### 2.2.2 Baseband

The mixer outputs are coupled to the baseband quadrature channel amplifier and filter stage, which is of 7th order topology. Operation and control of the baseband filter is contained in "Baseband Filter" on page 17.

The baseband paths are DC coupled, and include a DC correction loop. The high pass characteristic for the DC correction loop is defined by the off chip capacitor connected to pins 'IDC/IDC' and 'QDC/QDC'. The output of each channel stage is designed for low impedance drive capability and low intermodulation and can be loaded either differentially or single-ended; in the case of single-ended load the unused output should be unloaded. The maximum output load is defined in the electrical characteristics table.

# 2.3 RF bypass

The ZL10036 provides an independent bypass function, which can be used for driving a second receiver module. The electrical characteristics of the RF input are unchanged by the state of the RF bypass.

The bypass provides a differential buffered output from the input signal with a nominal 3.5 dB gain. The unused output should be terminated as in Figure 2 on page 2.

The bypass function is enabled by a single register bit and is not disabled by either the **PD** bit or the SLEEP pin. When disabled the bypass function is in a 'power-down' state. On power up the bypass function is enabled.

Figure 9 - RF input and Output (bypass) Return Losses

#### 2.4 Baseband Filter

The filter bandwidth is controlled by a Frequency Locked Loop (FLL) the timing of which is derived from the reference crystal source by a reference divider. Five control bits set the system reference division ratio and the baseband filter bandwidth can be programmed with a further six control bits for a nominal range of 4 - 40MHz<sup>1</sup>.

Figure 10 - Normalized Filter Transfer Characteristic (Setting 20 MHz)

The -3 dB bandwidth of the filter (Hz) is given by the following expression:  $_{f\text{-3dB}} = \frac{fxtal}{BR} \times (BF+1) \times \frac{1}{K}$  Where:

$f_{-3dB}$  = Baseband filter –3 dB bandwidth (Hz) which should be within the range 8MHz  $\leq$   $f_{-3dB} \leq$  35MHz.

$f_{xtal}$  = Crystal oscillator reference frequency (Hz).

K = 1.257 (constant).

BF = Decimal value of the register bits BF6:BF1, range 0 - 62.

BR = Decimal value of the bits BR4:BR0 (baseband filter reference divider ratio), range 4 - 27.

$\frac{f_{\text{xtal}}}{BR}$  = 575 kHz to 2.5 MHz.

Methods for determining the values of BR and BF are given in the section on software, please see 4.3, "Symbol Rate and Filter Calculations" on page 26.

<sup>1.</sup> specification compliant over the range 8 - 35 MHz.

#### 2.5 Local Oscillator

The LO on the ZL10036 is fully integrated and consists of three oscillator stages. These are arranged such that the regions of operation for optimum phase noise are contiguous over the required tuning range of 950 to 2150 MHz and over the specified operating ambient conditions and process spread.

The local oscillators operate at a harmonic of the required frequency and are divided down to the required LO conversion frequency. The required divider ratio is automatically selected by the LO control logic, hence programming of the required conversion frequency across the oscillator bands is automatic and requires no intervention by the user.

Figure 11 - LO Phase Noise Performance

The oscillators are designed to deliver good free running phase noise at 10 kHz offset, therefore the required integrated phase jitter from the LO can be achieved without the requirement for running with a high comparison frequency and hence large tuning increment and wide loop bandwidth.

## 2.6 PLL Frequency Synthesizer

The PLL frequency synthesizer section contains all the elements necessary, with the exception of a frequency reference and loop filter to control a varicap tuned LO, so forming a complete PLL frequency synthesized source. The device allows for operation with a high comparison frequency and is fabricated in high speed logic, which enables the generation of a loop with good phase noise performance. The loop can also be operated up to comparison frequencies of 2 MHz enabling application of a wide loop bandwidth for maximizing the close in phase noise performance. The LO conversion frequency is coupled to the 15-bit divider in the PLL frequency synthesizer.

The output of the programmable divider is fed to the phase comparator where it is compared with the comparison frequency. This frequency is derived either from the on-board crystal controlled oscillator or from an external reference source. In both cases the reference frequency is divided down to the comparison frequency by the reference divider, which is programmable into one of 29 ratios as detailed in Table 13 on page 25.

The typical application for the crystal oscillator is contained in Figure 2 on page 2. The output of the phase detector feeds a charge pump and loop amplifier section. This combined with an external loop filter integrates the current pulses into the varactor line voltage with an output range of Vee to VccTUNE. The varactor line voltage is externally coupled to the oscillator section through the input Vvar, enabling application of a third order loop.

Control of the charge pump current can be made as described in Table 12 on page 24.

## 2.7 Control Logic

The ZL10036 is controlled by an I<sup>2</sup>C data bus and can function as a slave receiver or slave transmitter compatible with 3V3 or 5 V levels.

Data and Clock are input on the SDA and SCL lines respectively as defined by  $I^2C$  bus standard. The device can either accept data (slave receiver, write mode), or send data (slave transmitter, read mode). The LSB of the address byte (R/W) sets the device into write mode if it is logic '0', and read mode if it is logic '1'. Table 4 and Table 6 illustrate the format of the read and write data respectively. The device can be programmed to respond to one of four addresses, which enables the use of more than one device in an  $I^2C$  bus system if required for use in  $PVR^1$  systems, for example. Table 3 shows how the address is selected by applying a voltage to the address, 'ADD', input. When the device receives a valid address byte, it pulls the SDA line low during the acknowledge period, and during following acknowledge periods after further data bytes are received. When the device is programmed into read mode, the controller accepting the data must pull the SDA line low during all status byte acknowledge periods to read another status byte. If the controller fails to pull the SDA line low during this period, the device generates an internal STOP condition, which inhibits further reading.

All the ZL10036 functions are controlled by register bits written through the I<sup>2</sup>C bus interface. The **SLEEP** pin can be used to power-down the device, but it can also be put into the power-down mode with the **PD** register bit, the two functions being logically OR'ed.

Feedback on the status of the ZL10036 is provided through eight bits in the status byte register, and the phase lock state is also available on the **LOCK** output pin (as well as the **FL** register bit).

#### 3.0 User Control

#### 3.1 I/O Pins

The I<sup>2</sup>C interface controls all the major functions in the ZL10036. Apart from the various analogue functions, the only pins that either control the ZL10036, or are controlled by the internal logic, are the **LOCK**, **SLEEP**, **P1**, **P0** and **ADD** pins. Details follow:

#### 3.1.1 LOCK - Pin 25

This is an output which indicates phase frequency lock for optimum phase noise. The CMOS output can directly drive a low power LED if required.

#### 3.1.2 SLEEP - Pin 11

The **SLEEP** pin shuts down the analogue sections of the device to give a considerable power saving, typically reducing the power to about one third of its normal level. The RF-bypass function is entirely separate and is unaffected by the state of this pin. The **SLEEP** pin's function is OR'ed with the **PD** register bit see 3.4.9, "Power Down (PD Bit)" on page 24, so that if either is a logic one, the ZL10036 will be powered down, or alternatively, both must be at logic zero for normal operation.

# 3.1.3 Output Ports, P1 & P0 - Pins 39 & 24

Two open-collector ports are provided for general purpose use, under control of register bits **P1** and **P0**. The default at power-up is for the **P1** & **P0** register bits to be low, hence the outputs will be off, i.e., in their high-impedance states. If connected to a pull-up resistor this will therefore result in a logic high. Setting a register bit high will turn the corresponding output on and therefore pull the logic level to near 0 V giving a logic low.

PVR - Personal Video Recorder where dual tuners allow the viewer to watch one channel and record another simultaneously, usually to a hard-disk recording system.

#### 3.2 Device Address Selection

Two internal logic levels, **MA1** and **MA0**, can be set to one of four possible logic states by the voltage applied to the **ADD** pin (#16). These four states in turn define four different read and write addresses on the I<sup>2</sup>C bus, so that as many as four separate devices can be individually addressed on one bus. This is of particular use in a multi-tuner environment as required by PVR applications.

| ADD Pin Voltage                  | MA1   | MA0   | Write Address |      | Read Address |      |

|----------------------------------|-------|-------|---------------|------|--------------|------|

| ADD FIII Voltage                 | IVIAI | IVIAU | Hex.          | Dec. | Hex.         | Dec. |

| Vee (0 V or Gnd)                 | 0     | 0     | 0xC0          | 192  | 0xC1         | 193  |

| Open circuit                     | 0     | 1     | 0xC2          | 194  | 0xC3         | 195  |

| 0.5 * DIGDEC (±20%) <sup>1</sup> | 1     | 0     | 0xC4          | 196  | 0xC5         | 197  |

| DIGDEC                           | 1     | 1     | 0xC6          | 198  | 0xC7         | 199  |

Table 3 - Address Selection

# 3.3 Read Register

The ZL10036 status can be read by addressing the device in its slave transmitter mode by setting the LSB of the address byte (the R/W bit) to a one. After the master transmits the correct address byte, the ZL10036 will acknowledge its address, and transmit data in response to further clocks on the SCL input. If the master responds with an acknowledge and further clocks, the status byte will be retransmitted until such time as the master fails to send an acknowledge, when the ZL10036 will release the data bus, allowing the master to generate a stop condition.

| Bit No. | 7<br>(MSB) | 6  | 5 | 4 | 3 | 2   | 1   | 0<br>(LSB) |

|---------|------------|----|---|---|---|-----|-----|------------|

| Address | 1          | 1  | 0 | 0 | 0 | MA1 | MA0 | 1          |

| Status  | POR        | FL | Х | Х | Х | Х   | Χ   | Х          |

Table 4 - Read Data Bit Format (MSB is Transmitted First)

The individual bits in the status register have the following meanings:

## 3.3.1 Power-On Reset Indicator (POR bit)

This bit is set to a logic '1' if the VccDIG supply to the PLL section has dropped below typically 3.6 V, e.g., when the device is initially turned on. The bit is reset to '0' when the read sequence is terminated by a STOP command. When the POR bit is high, this indicates that the programmed information may have been corrupted and the device reset to power up condition.

## 3.3.2 Frequency & Phase Lock (FL bit)

Bit 6 (FL) indicates whether the synthesizer is phase locked, a logic '1' is present if the device is locked, and a logic '0' if the device is unlocked.

<sup>1.</sup> can be programmed with a single 30  $k\Omega$  resistor to DIGDEC

# 3.3.3 Internal Operation Indicators (X Bits)

These bits indicate internal logic states and are not required for normal use of the ZL10036.

#### 3.4 Write Registers

The ZL10036 has twelve registers which can be programmed by addressing the device in its slave receiver mode, setting the LSB of the address byte (the R/W bit) to a zero. After the master transmits the correct address byte, the ZL10036 will acknowledge its address, and accept data in response to further clocks on the SCL line. At the end of each byte, the ZL10036 will generate the acknowledge bit. The master can at this point, generate a stop condition, or further clocks on the SCL line if further registers are to be programmed. If data is written after the twelfth register (byte-13), it will be ignored.

# 3.4.1 Register Sub-Addressing

If some register bits require changing, but not all, it is not necessary to write to all the registers. The registers can be addressed in pairs starting with the even numbered bytes, i.e., 2 & 3, 4 & 5, etc. Table 5 below shows the protocol required to address any of the even numbered register bytes. It therefore follows that to write to register byte-7 for instance, byte-6 must also be written first. Register pairs may be written in any order, as required by the software, e.g., 10/11 may be followed by 4/5.

| Da                                                 | ta Bi |   |   |               |  |  |  |

|----------------------------------------------------|-------|---|---|---------------|--|--|--|

| <b>7</b> (MSB)                                     |       |   | 4 | Byte Selected |  |  |  |

| 0                                                  | Χ     | Χ | Χ | 2             |  |  |  |

| 1                                                  | 0     | Х | Х | 4             |  |  |  |

| 1                                                  | 1     | 0 | 0 | 6             |  |  |  |

| 1                                                  | 1     | 0 | 1 | 8             |  |  |  |

| 1                                                  | 1     | 1 | 0 | 10            |  |  |  |

| 1                                                  | 1     | 1 | 1 | 12            |  |  |  |

| 'X' = Don't care (content defines a register bit). |       |   |   |               |  |  |  |

Table 5 - Byte Address Allocation in Write Mode

# 3.4.2 Register Mapping

| Byte | Bit No.<br>Function | <b>7</b> (MSB)        | 6              | 5                     | 4                      | 3                     | 2                     | 1                     | <b>0</b> (LSB)        | Reset<br>state<br>(hex.) 1 | Further information         |

|------|---------------------|-----------------------|----------------|-----------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------------|-----------------------------|

| 1    | Device address      | 1                     | 1              | 0                     | 0                      | 0                     | MA1                   | MA0                   | 0                     |                            | Table 3 on page 20          |

| 2    | Programmable        | 0                     | 214            | 2 <sup>13</sup>       | <b>2</b> <sup>12</sup> | 2 <sup>11</sup>       | 2 <sup>10</sup>       | <b>2</b> <sup>9</sup> | <b>2</b> <sup>8</sup> | 0x00                       | Can 2.4.2 an mana 22        |

| 3    | Divider             | <b>2</b> <sup>7</sup> | 2 <sup>6</sup> | <b>2</b> <sup>5</sup> | 2 <sup>4</sup>         | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>        | <b>2</b> <sup>0</sup> | 0x00                       | See 3.4.3 on page 23        |

| 4    |                     | 1                     | 0              | RFG                   | BA1                    | BA0                   | BG1                   | BG0                   | LEN                   | 0x80                       | "3.4.4" to "3.4.7" on p. 24 |

| 5    |                     | P0                    | C1             | C0                    | R4                     | R3                    | R2                    | R1                    | R0                    | 0x00                       | pp. 24, 24 & 25             |

| 6    |                     | 1                     | 1              | 0                     | 0                      | RSD                   | 0                     | 0                     | 0                     | 0xC0                       | see "3.4.13" on page 25     |

| 7    |                     | P1                    | BF6            | BF5                   | BF4                    | BF3                   | BF2                   | BF1                   | 0                     | 0x20                       | pp. 24 & 25                 |

| 8    | Control Data        | 1                     | 1              | 0                     | 1                      | 0                     | 0                     | 1                     | 1                     | 0xDB                       | page 26                     |

| 9    | Control Data        | 0                     | 0              | 1                     | 1                      | 0                     | 0                     | 0                     | 0                     | 0x30                       | page 26                     |

| 10   | 0                   | 1                     | 1              | 1                     | 0                      | 0                     | 0                     | 0                     | 1                     | 0xE1                       | page 26                     |

| 11   |                     | U <sup>2</sup>        | 1              | 1                     | 1                      | 0                     | 1                     | 0                     | 1                     | 0x75/F5                    | page 26                     |

| 12   |                     | 1                     | 1              | 1                     | 1                      | 0                     | 0                     | 0                     | 0                     | 0xF0                       | test function only          |

| 13   |                     | PD                    | BR4            | BR3                   | BR2                    | BR1                   | BR0                   | CLR                   | TL                    | 0x28                       | pp. 24, 25 & 25             |

Table 6 - Bit Allocations in the Write Registers

- 1. This is the power-on default register value recommended operating values may be different, see "4.1" on page 26.

- 2. This bit is undefined at power up as its level determines different functions for the other bits in this register.

| Symbol | Definition                                     | Symbol  | Definition                      |  |  |

|--------|------------------------------------------------|---------|---------------------------------|--|--|

| 214-20 | Programmable division ratio control bits       | MA1,MA0 | Variable address bits           |  |  |

| BA1-0  | Baseband prefilter gain adjust                 | P0, P1  | External switching ports        |  |  |

| BF6-1  | Baseband bandwidth adjust                      | PD      | Power down                      |  |  |

| BG1-0  | Baseband postfilter gain adjust                | R4-R0   | Reference division ratio select |  |  |

| BR4-0  | Baseband filter FLL reference frequency select | RFG     | RF programmable gain adjust     |  |  |

| C1,C0  | Charge pump current select                     | RSD     | Resistor switch disable         |  |  |

| CLR    | Control logic reset                            | TL      | Buffered LO output select       |  |  |

| LEN    | RF bypass enable                               |         |                                 |  |  |

Table 7 - Key to Table 6

# 3.4.3 Synthesizer Division Ratio (2<sup>14</sup>:2<sup>0</sup> Bits)

The PLL synthesizer interfaces with the LO multiplex output and runs at the desired frequency for down-conversion. The step size at the desired conversion frequency, is equal to the loop comparison frequency.

The programmable division ratio, 2<sup>14</sup> to 2<sup>0</sup>, required for a desired conversion frequency, can be calculated from the following formula:

Desired conversion frequency =  $\Delta f$ step  $\times$  (2<sup>14</sup> + 2<sup>13</sup> + 2<sup>12</sup>  $\rightarrow$  2<sup>2</sup> + 2<sup>1</sup> + 2<sup>0</sup>)

where:  $\Delta f$ step = Fcomp

# 3.4.4 RF Gain (RFG Bit)

The RF gain is programmed by setting the **RFG** bit, bit-5 of register byte-4 as required. See also Figure 4, "AGC Control Structure" on page 13.

| RFG | Gain Adjust (dB) |               |

|-----|------------------|---------------|

| 0   | 0                | (reset state) |

| 1   | +4               |               |

Table 8 - RFG Register Bit Function

# 3.4.5 Baseband Pre-Filter Gain Adjust (BA1:0 Bits)

The baseband pre-filter gain is programmed by setting **BA1:0**, bits-4 & 3 of register byte-4 as required. See also Figure 4, "AGC Control Structure" on page 13.

| BA1 | BA0 | Pre-Filter Gain Adjust (dB) |               |

|-----|-----|-----------------------------|---------------|

| 0   | 0   | 0.0                         | (reset state) |

| 0   | 1   | +4.2                        |               |

| 1   | 0   | +8.4                        |               |

| 1   | 1   | +12.6                       |               |

Table 9 - BA1/0 Register Bits Function

# 3.4.6 Baseband Post-Filter Gain (BG1:0 Bits)

The baseband post-filter gain is programmed by setting **BG1:0**, bits-2 & 1 of register byte-4 as required. See also Figure 4, "AGC Control Structure" on page 13.

| BG1 | BG0 | Post-Filter Gain Adjust (dB) |               |

|-----|-----|------------------------------|---------------|

| 0   | 0   | 0.0                          | (reset state) |

| 0   | 1   | +4.2                         |               |

| 1   | 0   | +8.4                         |               |

| 1   | 1   | +12.6                        |               |

Table 10 - BG1/0 Register Bits Function

## 3.4.7 RF Bypass Disable (LEN Bit)

The RF bypass function is disabled by setting **LEN**, bit-0 of register byte-4 to a logic '1'. By default, this bit is at a logic '0' at power-up, and therefore the function is enabled. If the function is not required, a power saving of approximately 15% can be made by setting this bit. See also section 2.3 on page 16.

# 3.4.8 Output Port Controls (P1 & P0 Bits)

Register bits **P1** and **P0**, bit-7 in register bytes-7 & 5 respectively, control the output port pins, P1 & P0, pin numbers 39 & 24 respectively.

| Bit P1 or P0 | Port State                 | Logic State (if connected to a pull-up) |               |

|--------------|----------------------------|-----------------------------------------|---------------|

| 0            | High impedance             | 1                                       | (reset state) |

| 1            | Low impedance to Vee (Gnd) | 0                                       |               |

**Table 11 - Port Control Bits**

# 3.4.9 Power Down (PD Bit)

Bit-7 of byte-13 controls the **PD** register bit which is an alternative to the SLEEP pin (see "SLEEP - Pin 11" on page 19). Setting the **PD** bit to a logic '1' shuts down the analogue sections of the ZL10036 effecting a saving of about two thirds of the power required for normal operation. A logic '0' restores normal operation. With either hardware or software power-down, all register settings are unaffected.

# 3.4.10 Logic Reset (CLR Bit)

Bit-1 of byte-13 controls the **CLR** register bit. When set to a logic '1', this self-clearing bit resets the ZL10036 control logic. Writing a logic '0' has no effect. The following register numbers are reset to their power-on state: 7, 9, 10, 11, 12 & 13. All other register's contents are unaffected.

## 3.4.11 Charge Pump Current (C1 & C0 Bits)

Register bits **C1** and **C0** are programmed by setting bits-6 & 5 of register byte-5. These bits determine the charge pump current that is used on the output of the frequency synthesizer phase detector.

| C1 | CO | Ci   |            |      |               |

|----|----|------|------------|------|---------------|

| Ci | CU | Min. | Тур.       | Max. |               |

| 0  | 0  | ±160 | ±210       | ±290 | (reset state) |

| 0  | 1  | ±280 | ±365       | ±510 |               |

| 1  | 0  | ±470 | ±625       | ±860 |               |

| 1  | 1  | N    | lot allowe |      |               |

**Table 12 - Charge Pump Currents**

# 3.4.12 Reference Division Ratios (R4:0 Bits)

Register bits **R4:0** control the reference divider ratios as shown in Table 13. They are programmed through bit-4 to bit-0 respectively, in byte-5.

|    |    | R4 | 0               | 0   | 1         | 1   |  |  |  |

|----|----|----|-----------------|-----|-----------|-----|--|--|--|

| R3 |    | R3 | 0 1             |     | 0         | 1   |  |  |  |

| R2 | R1 | R0 | Division Ratios |     |           |     |  |  |  |

| 0  | 0  | 0  | 2               | III | egal stat | es  |  |  |  |

| 0  | 0  | 1  | 4               | 5   | 6         | 7   |  |  |  |

| 0  | 1  | 0  | 8               | 10  | 12        | 14  |  |  |  |

| 0  | 1  | 1  | 16              | 20  | 24        | 28  |  |  |  |

| 1  | 0  | 0  | 32              | 40  | 48        | 56  |  |  |  |

| 1  | 0  | 1  | 64              | 80  | 96        | 112 |  |  |  |

| 1  | 1  | 0  | 128             | 160 | 192       | 224 |  |  |  |

| 1  | 1  | 1  | 256             | 320 | 384       | 448 |  |  |  |

Table 13 - Division Ratios Set with Bits R4 - R0

# 3.4.13 Baseband Filter Resistor Switching (RSD)

The baseband filters use a resistor switching technique that improves bandwidth and phase matching between the I and Q channels. The bandwidth range is effectively separated into 3 sub-ranges with different resistor values being used in each sub-range. It is possible for the filter bandwidth accuracy to be degraded if the bandwidth setting happens to coincide with one of the two transition points between these regions. This can be overcome by disabling the resistor switching using the **RSD** bit. For optimum filter performance the **RSD** bit should first be enabled so that the correct resistor value is automatically set for the selected bandwidth.

The **RSD** bit (bit-3 of byte-6) controls the resistor switching. With the default setting of logic '0' it is enabled and the correct resistor value automatically chosen. With the **RSD** bit set to a logic '1' then the switching is disabled and this freezes the resistors at their chosen value. The procedure when selecting a new bandwidth setting is to enable then disable the switching; set **RSD** to logic '0' then to logic '1'.

# 3.4.14 Baseband Filter Bandwidth (BF6:1 & BR4:0 Bits)

Bits 6 to 1 of byte-7 configure bits **BF6** to **BF1** respectively. These bits set a decimal number in the range 0 to 62 (63 is not allowed) to determine the baseband filter bandwidth in conjunction with other values.

Bits 6 to 2 of byte-13 configure bits **BR4** to **BR0** respectively. These bits set the reference divider ratio for the baseband filter. A number in the range 4 to 27 inclusive (values outside this range are not allowed) can be set, with the proviso that the value of fxtal/BR4:0 must also be in the range 575 kHz to 2,500 kHz.

For further details, please also see 2.4, "Baseband Filter" on page 17 and "Symbol Rate and Filter Calculations" (sect. 4.3) on page 26.

# 3.4.15 LO Test (TL Bit)

For test purposes, the LO clock divided by the prescaler ratio can be output on the LOTEST pin by setting bit **TL** (byte-13 bit-0) to a logic '1'. By default this output is off, i.e., the **TL** bit is at logic '0'.

#### 4.0 Software

In normal operation, only initialization, channel (frequency) changes and symbol rates require programming intervention. Note that the PLL comparison frequency is set by the crystal frequency divided by the PLL reference divide ratio. In the following examples of register settings, binary values are frequently used, indicated as e.g.,  $0110_2$ .

#### 4.1 Power-on Software Initialization

- a. Bytes 2 + 3:  $2^{14}$   $2^{0}$  = desired channel frequency/PLL comparison frequency.

- b. Byte 4: BA1:0 =  $01_2$  for initial baseband filter input level.

- c. **Byte 4:** BG1:0 =  $01_2$  for target baseband filter output level.

- d. Byte 4: LEN = 1 if the RF loop through is to be disabled.

- e. Byte 5: R4:0 = PLL reference divider for desired comparison frequency.

- f. Bytes 8 10: should be set to the following values: 0xD3, 0x40 & 0xE3 respectively.

- g. **Byte 11:** this should be written twice with the following values:0x5B & 0xF9. The order in which these values are written is not important.

- h. **Byte 13:** BR4:0 = Crystal frequency in use (see also 4.3.3.1 on page 27).

# 4.2 Changing Channel

Bytes 2 + 3: 2<sup>14</sup> - 2<sup>0</sup> = Channel frequency/PLL comparison frequency.

# 4.3 Symbol Rate and Filter Calculations

#### 4.3.1 Determining the Filter Bandwidth from the Symbol Rate

$f_{bw} = (\alpha * symbol rate)/(2.0 * 0.8) + f_{offs}$

where:

$\alpha$  = 1.35 for DVB or 1.20 for DSS, and is the roll-off of the raised-root cosine filter in the transmitter,

foffs is the total offset of the received signal due to all causes (LNB drift, synthesizer step size, etc) and is read back from the demodulator (ZL10036),

and f<sub>bw</sub> is the -3 dB roll-off of the filter for:  $8 \text{ MHz} \le f_{bw} \le 35 \text{ MHz}$ .

For low symbol rates, the energy content within the bandwidth of the filters reduces significantly so incrementing the baseband post-filter gain helps recover the signal level for the demodulator.

N.B. During channel acquisition or re-acquisition, the filter must be set to its maximum value.

# 4.3.2 Calculating the Filter Bandwidth

The -3 dB bandwidth of the filter (Hz) is given by the following expression:

Equation 1 -

$$f_{bw} = \frac{f_{xtal}}{BR} \times (BF + 1) \times \frac{1}{K}$$

Where:

$f_{\text{bw}}$  = Baseband filter -3 dB bandwidth (Hz) which should be within the range  $8\text{MHz} \le f_{\text{bw}} \le 35\text{MHz}$ .

$f_{xtal}$  = Crystal oscillator reference frequency (Hz).

K = 1.257 (constant).

BF = Decimal value of the register bits BF6:BF1, range 0 - 62.

BR = Decimal value of the bits BR4:BR0 (baseband filter reference divider ratio), range 4 - 27.

where: 575 kHz

$$\leq \frac{f_{xtal}}{BR} \leq 2.5$$

MHz.

The digital nature of the control loop means that the filter bandwidth setting is quantized: the difference between the desired filter bandwidth and the actual filter bandwidth possible due to discrete settings causes a bandwidth error. In order to minimize this bandwidth error, the maximum filter bandwidth setting resolution is needed. From the limits given above, the best resolution possible is 575 kHz/1.257 = 457.4 kHz. However if this resolution is used, the maximum bandwidth with BF = 62 is only 28.82 MHz, below the maximum of 35 MHz. Therefore for filter bandwidths greater than 28.82 MHz the resolution must be decreased. For filter bandwidths around 35 MHz the resolution is typically reduced to 698 kHz/1.257 = 555.3 kHz.

# 4.3.3 Determining the Values of BF and BR

## 4.3.3.1 Calculating the Value of BR

The above description can be described mathematically as:

For  $f_{bw} \le 28.82MHz$ ,

**Equation 2 -** BR =

$$\frac{f_{xtal}}{575kHz}$$

.

For  $f_{bw} > 28.82MHz$ ,

Equation 3 - BR =

$$\frac{f_{xtal}}{f_{bw}} \times (62 + 1) \times \frac{1}{K}$$

.

These equations can give non-integer results so rounding must be performed. The values for BR should be rounded DOWN to the nearest integer this ensures that  $\frac{f_{xtal}}{BR}$  will not be below 575 kHz and that the maximum programmable bandwidth will not be below the desired bandwidth due to rounding.

## 4.3.3.2 Calculating the Value of BF

Equation 4 - BF =

$$\left(\frac{f_{bw}}{f_{ytal}} \times BR \times K\right) - 1 =$$

For non-integer values of BF, the result should be simply rounded to the nearest integer to give the value for BF6:1.

# 4.3.4 Filter Bandwidth Programming Examples

**Example 1, conditions:**  $f_{xtal} = 10.111MHz$ ,  $f_{bw} = 9MHz$

Because f<sub>bw</sub> is below 28.2MHz, the value of BR can be evaluated with equation 2:

BR =

$$\frac{f_{xtal}}{575kHz}$$

=  $\frac{10.111MHz}{575kHz}$  = 17.583

This result should be rounded down to 17 to ensure that the result is not below the 575 kHz limit. Using this value for BR, equation 4 can be evaluated:

BF =

$$\left(\frac{f_{bw}}{f_{xtal}} \times BR \times K\right) - 1 = \left(\frac{9MHz}{10.11MHz} \times 17 \times 1.257\right) - 1 = 18.02285$$

The result can be rounded to the nearest value, i.e., BF = 18.

**Example 2, conditions:**  $f_{xtal} = 10.111MHz$ ,  $f_{bw} = 34.6MHz$

In this case,  $f_{bw}$  is above 28.2MHz so using equation 3 to solve for BR:

$$BR = \frac{f_{xtal}}{f_{bw}} \times (63) \times \frac{1}{K} = \frac{10.111MHz}{34.6MHz} \times (63) \times \frac{1}{1.257} = 14.647$$

Using equation 4, this time with the rounded-down value of 14 for BR:

BF =

$$\left(\frac{f_{bw}}{f_{xtal}} \times BR \times K\right) - 1 = \left(\frac{34.6MHz}{10.11MHz} \times 14 \times 1.257\right) - 1 = 59.227$$

Rounding to the nearest integer thus gives a value of 59 for BF.

# 4.4 Programming Sequence for Filter Bandwidth Changes

- a. Byte 6: Set RSD = 0 to re-enable baseband filter resistor switching.

- b. Byte 7: Set BF6:1 to the value derived in 4.3.3.2, "Calculating the Value of BF" on page 27.

- c. **Byte 6:** Set RSD = 1 to disable baseband filter resistor switching. This must happen no sooner than a certain time after (b.). This minimum time equals BR/(32 \* fxtal) seconds, where BR is the decimal value of byte BR and fxtal is the reference crystal frequency.

# 5.0 Application Notes

# 5.1 Thermal Considerations

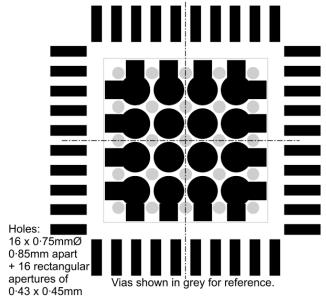

Figure 12 - Copper Dimensions for Optimum Heat Transfer

Figure 13 - Paste Mask for Reduced Paste Coverage

The ZL10036 uses the 40-pin QFN package with a thermal 'paddle' in the base, which has a very high thermal conductivity to the die, as well as low electrical resistance to the Vee connections. The ZL10036 has a fairly high power density, and if the excess heat is not efficiently removed, it will rapidly overheat beyond the 125°C limit, and affect the performance or could even cause permanent damage to the device.

The paddle is designed to be soldered to a size-matched pad on the PCB (see Figure 13 on page 29) which is thermally connected to an efficient heat sink. The heat sink can be as simple as an area of copper ground plane on

the underside of the board, thereby reducing the system cost. To transfer the heat from the paddle to the underside of the board, an array of  $25 \times 0.3 \text{ mm} \emptyset$  vias are used between the topside pad, which will be soldered to the paddle, and the ground plane on the underside of the board. It is also possible to use a smaller number of larger vias, e.g.  $16 \times 0.5 \text{ mm} \emptyset$ , but this arrangement is marginally less efficient.

The area of copper in the ground plane must be at least 2,000 mm<sup>2</sup> for 1 oz copper. If 2 oz copper board is used or if multiple ground planes are available, as with a four-layer board, the area could be reduced somewhat, but in general it is better to have the maximum cooling possible, as reliability will always be enhanced if lower temperatures are maintained.

While it is possible to use a paste mask that simply duplicates the aperture for the 4.15 mm sq. paddle, the quantity of solder paste under the device can cause problems and it is preferable to reduce the coverage to a level between 50% and 80% of the area. The pattern shown in Figure 14 on page 30 reduces the coverage to approximately 60%, which should reduce out-gassing from under the device and improve the stand-off height of the package from the board.

A very useful publication giving further details is: "Application Notes for Surface Mount Assembly of Amkorbs MicroLeadFrame (MLF) Packages" which can be found on: www.amkor.com

# 5.2 Crystal Oscillator Notes

| Component                                                                 | 4 MHz | 10.111 MHz |  |  |  |  |  |

|---------------------------------------------------------------------------|-------|------------|--|--|--|--|--|

| C10                                                                       | 47 pF | 100 pF     |  |  |  |  |  |

| C11                                                                       | 47 pF | 100 pF     |  |  |  |  |  |

| C12* 10 pF 15 pF                                                          |       |            |  |  |  |  |  |

| * C12 may be replaced by a link to GND if crystal output is not required. |       |            |  |  |  |  |  |

Table 14 - Crystal Capacitor Values for 4 MHz and 10.111 MHz Operation

(component numbering refers to the example schematic, Figure 2 on page 2)

The 10.111 MHz frequency recommended for the crystal, is chosen such that when used with the Zarlink ZL10312 demodulator, the system frequency is 91 MHz = 9 \* 10.111 MHz (91 MHz > 2 \* 45 Ms/s).

Figure 14 - Typical Oscillator Arrangement with Optional Output

Figure 15 - Typical Arrangement for External Oscillator

# 6.0 Electrical characteristics

# 6.1 Test Conditions

The following conditions apply to all figures in this chapter, except where notes indicate other settings.

Tamb =  $-10^{\circ}$  to  $85^{\circ}$ C, Vee= 0 V, All Vcc supplies =  $5 \text{ V} \pm 5\%$

RF gain adjust = +0 dB, prefilter = +4.2 dB and postfilter = 4.2 dB. RFG=0, BA1=0, BA0=1, BG1=0, BG0=1

These characteristics are guaranteed by either production test or design. They apply within the specified ambient temperature and supply voltage unless otherwise stated.

# 6.2 Absolute Maximum Ratings

| Parameter                                                      | Symbol                                  | Min. | Max.        | Unit | Notes                               |

|----------------------------------------------------------------|-----------------------------------------|------|-------------|------|-------------------------------------|

| Supply voltage                                                 | VccBB, VccDIG, VccLO,<br>VccRF, VccTUNE | -0.3 | 5.5         | ٧    | w.r.t. Vee                          |

| Storage temperature                                            | T <sub>STG</sub>                        | -55  | 150         | °C   |                                     |

| Junction temperature                                           | T <sub>j</sub>                          |      | 125         | °C   |                                     |

| Voltage on SDA & SCL                                           |                                         | -0.3 | 6           | V    | Vcc = Vee to 5.25 V                 |

| Voltage on DRIVE                                               |                                         | -0.3 | VccTUNE+0.3 | V    |                                     |

| Voltage on RFIN, RFBYPASS and inverted equivalents             |                                         | -0.3 | VccRF+0.3   | V    |                                     |

| Voltage on RFAGC                                               |                                         |      |             |      |                                     |

| Voltage on Vvar                                                |                                         | 0.0  | VccLO+0.3   | .,   |                                     |

| Voltage on LOTEST                                              |                                         | -0.3 | VCCLO+0.3   | V    |                                     |

| Voltage on IOUT, QOUT, IDC,<br>QDC and inverted<br>equivalents |                                         | -0.3 | VccBB+0.3   | V    |                                     |

| Voltage on P1                                                  |                                         |      |             |      |                                     |

| Voltage at DIGDEC                                              |                                         | -0.3 | 3.6         | V    |                                     |

| Voltage on PUMP                                                |                                         | 0.3  | VccDIG+0.3  | V    |                                     |

| Voltage on SLEEP and P0                                        |                                         | -0.3 | VCCDIG+0.3  | V    |                                     |

| Voltage on ADD, XTAL,<br>XTALCAP and LOCK                      |                                         | -0.3 | DIGDEC+0.3  | ٧    |                                     |

| Sink current, P0 or P1                                         |                                         |      | 20          | mA   | Each output                         |

| ESD protection, pins 31 & 32 <sup>1</sup>                      |                                         | 0.5  |             | kV   | To Mil-std 883B<br>method 3015 cat1 |

| pins 1-30, 33-40                                               |                                         | 2.0  |             | kV   |                                     |

<sup>1.</sup> ESD protection can be increased by adding a protection diode (D1) to the input circuit as shown in the application circuit (Figure 2).

# **6.3 Recommended Operating Conditions**

| Parameter             | Symbol                               | Min. | Max. | Unit | Notes      |

|-----------------------|--------------------------------------|------|------|------|------------|

| Supply voltage        | VccBB, VccDIG, VccLO, VccRF, VccTUNE | 4.75 | 5.25 | V    | w.r.t. Vee |

| Operating temperature | T <sub>OP</sub>                      | -10  | 85   | °C   |            |

# 6.4 DC Characteristics

| Pins                                        | Characteristic              | Min. | Тур. | Max. | Units    | Cond                                                                                                                  | itions          |  |  |  |

|---------------------------------------------|-----------------------------|------|------|------|----------|-----------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

|                                             | Normal operating conditions |      |      |      |          |                                                                                                                       |                 |  |  |  |

|                                             |                             |      |      |      |          | RF bypass                                                                                                             | filter b.w.     |  |  |  |

|                                             |                             |      | 210  | 259  | mA       | disabled                                                                                                              | minimum         |  |  |  |

| All Vcc pins:                               |                             |      | 228  | 281  | mA       | disabled                                                                                                              | maximum         |  |  |  |

| 5, 6, 18, 19,<br>26, 29, 36,                | Supply current              |      | 243  | 300  | mA       | enabled                                                                                                               | minimum         |  |  |  |

| 37                                          |                             |      | 261  | 322  | mA       | enableu                                                                                                               | maximum         |  |  |  |

|                                             |                             |      | 82   | 107  | mA       | disabled                                                                                                              | sleep mode      |  |  |  |

|                                             |                             |      | 115  |      | mA       | enabled                                                                                                               | sleep mode      |  |  |  |

|                                             | Output impedance            |      | 25   |      | Ω        | Single-ended                                                                                                          |                 |  |  |  |

| QOUT,<br>QOUT, IOUT,<br>IOUT: 3, 4, 7,<br>8 | Output load                 | 1    |      | 15   | kΩ<br>pF | Maximum load, which can be applied to output, single-ended. If operated single ended unused output should be unloaded |                 |  |  |  |

| QDC, QDC,                                   | Bias voltage                |      | 3.8  |      | V        |                                                                                                                       |                 |  |  |  |

| IDC, IDC: 1,<br>2, 9, 10                    | Output impedance            |      | 11   |      | kΩ       |                                                                                                                       |                 |  |  |  |

|                                             | Input high voltage          | 2.3  |      | 5.5  | V        |                                                                                                                       |                 |  |  |  |

|                                             | Input low voltage           | 0    |      | 1    | V        |                                                                                                                       |                 |  |  |  |

| SCL, SDA:<br>12, 13                         | Input current               | -10  |      | 10   | μΑ       | Input voltage = VccDIG                                                                                                | =Vee to         |  |  |  |

| ,                                           | Leakage current             |      |      | 10   | μA       | Input voltage = VccDIG=Vee                                                                                            | = Vee to 5.5 V, |  |  |  |

|                                             | Hysteresis                  |      | 0.4  |      | V        |                                                                                                                       |                 |  |  |  |

| SDA: 13                                     | Output voltage              |      |      | 0.4  | V        | Isink = 3 mA                                                                                                          |                 |  |  |  |

| SDA. 13                                     |                             |      |      | 0.6  | V        | Isink = 6 mA                                                                                                          |                 |  |  |  |

| DUMP: 04                                    | Charge pump<br>leakage      |      | +-3  | +-20 | nA       | Vpin = 1.8 V                                                                                                          |                 |  |  |  |

| PUMP: 21                                    | Charge pump current         |      |      |      |          | Vpin = 1.8 V. S<br>on page 24                                                                                         | See Table 12    |  |  |  |

| Pins                        | Characteristic             | Min.        | Тур. | Max. | Units | Cond                                                          | litions           |  |

|-----------------------------|----------------------------|-------------|------|------|-------|---------------------------------------------------------------|-------------------|--|

| DDI\/E. 20                  | Max. voltage               | VccTUNE-0.2 |      |      | ٧     | On-chip 3 kohm load resisto to VccTUNE                        |                   |  |

| DRIVE: 20                   | Min. voltage               |             |      | 0.3  | ٧     |                                                               |                   |  |

| XTAL,<br>XTALCAP:<br>14, 15 | Recommended crystal E.S.R. | 10          |      | 200  | Ω     | Parallel resonant crystal                                     |                   |  |

| Vvar: 23                    | Input current              | -1          |      | 1    | mA    | Vee <= Vvar <= 1.7 V<br>(on-chip varactors forward<br>biased) |                   |  |

|                             |                            | -25         |      | 25   | μΑ    | 1.7 V <= Vvar <= Vcc                                          |                   |  |

| P0, P1: 24,                 | Sink current               | 10          |      |      | mA    | At Vport = 0.7                                                | V                 |  |

| 39                          | Leakage current            |             |      | 10   | μΑ    | Vport = Vcc                                                   |                   |  |

|                             | Low output voltage         |             |      | 0.5  | V     | Out of lock                                                   | at 1 mA           |  |

| LOCK: 25                    | High output voltage        | DigDec-0.5  |      |      | V     | In lock                                                       | atriiiA           |  |